Merhaba sevgili ziyaretçiler MOSFET Nedir başlıklı yazımızda Alan Etkili Tranzistörler (FET) konusuna giriş yapmış ne olduğundan bahsetmiştik. Bu yazımızın konusu ise JFET olacak. FET’ler Gate ucundan verilen gerilim yoluyla oluşturulan elektrik alan ile source ve drain arasındaki gerilimin kontrol edilebildiği elektronik parçalardır.

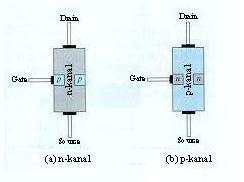

JFET ise, kanaldaki akımı kontrol etmek için ters kutuplanmış bir ekleme sahip olan bir Alan Etkili Transistör çeşididir. JFET sembolleri aşağıda üstteki çizimde gösterilmiştir. JFET yapısına göre, n-kanal ve p-kanal olmak üzere ikiye ayrılır. Alttaki çizimde (a) ve (b) de bu her iki tip JFET görülmektedir. (a) daki n-kanal JFET’te n tipi kanalın her iki ucuna birer tel bağlanır ve üsttekine drain (akıntı), alttakine ise source (kaynak) adı verilir. N tipi maddede bir kanal oluşturmak için iki p tipi bölge yayılır. Bu her iki p tipi bölge gate (kapı) adını verdiğimiz uca bağlanır. Şekilde kolaylık açısından iki p tipi bölgenin bağlantısı yerine sadece bir bağlantı gösterilmiştir.

JFET’İN ÇALIŞMASI

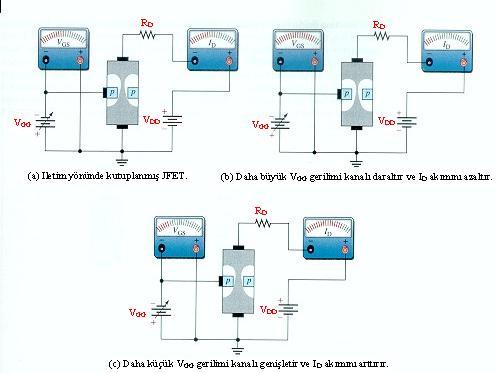

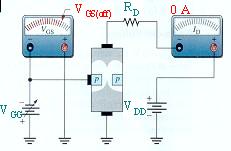

JFET’in çalışmasını aşağıdaki şekilde gösterilen n-kanal JFET üzerinde açıklayalım. VDD gerilimi drain-source voltajını sağlar ve drain’den source’a akan akımı oluşturur. VGG gerilimi de gate-source arasındaki ters kutuplama voltajını sağlar.

JFET her zaman gate-source pn ekleminin ters kutuplanmasıyla çalıştırılır. Gate-source ekleminin negatif bir gerilimle ters kutuplanması n-kanalda fakirleşmiş bir bölge oluşturur ve direncini arttırır. Kanal genişliği, gate voltajı ayarlanarak kontrol edilebilir ve böylece ID drain akımı da kontrol edilebilir. Bu işlemler şekildeki (b) ve (c) de gösterilmiştir.

Gate bölgesindeki p tipi malzemeyi çeviren beyaz alanlar, ters kutuplama ile oluşan fakirleşmiş bölgeyi temsil eder. Bu fakirleşmiş bölge, kanalın drain ucuna doğru daha geniştir, çünkü gate ve drain arasındaki ters kutuplama gerilimi, gate ve source arasındaki gerilimden daha büyüktür.

JFET KARAKTERİSTİKLERİ

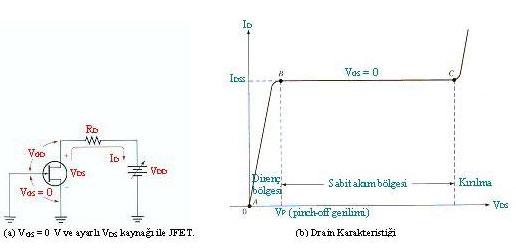

İlk olarak gate-source voltajı sıfır (VGS=0 V) olarak alınır. Bu voltaj değeri gate ucunu source ucuna bağlayarak elde edilir.

Aşağıdaki şekilde (a) da olduğu gibi her iki uçta toprağa bağlanır. VDD (yani VDS) 0 volttan itibaren artarken ID akımı da belli oranda artacaktır, (b) deki grafiğin A ve B noktaları arasında gösterildiği gibi. Bu bölgede kanal direnci sabittir çünkü fakirleşmiş bölge yeterli etkiye sahip olacak kadar büyük değildir. Bu bölge direnç bölgesi olarak adlandırılır çünkü VDS ve ID ohm kanunuyla bağlantılıdır.

Yukarıdaki şekil (b) de B noktasında eğim sıfırdır ve ID akımı sabittir. VDS gerilimi B noktasından C noktasına artarken, gate-drain ters kutuplama voltajı (VGD), VGS gerilimindeki artışı dengeleyecek kadar büyük bir fakirleşmiş bölge oluşturur, böylece ID akımı sabit tutulur.

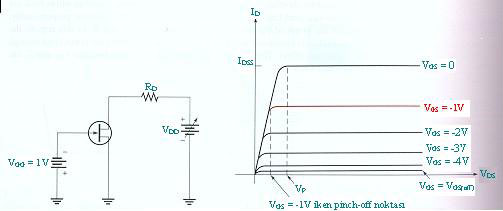

PİNCH-OFF GERİLİMİ

VGS = 0V için, ID akımının sabit hale geçtiği Yukarıda şekilde (b) deki Drain Karakteristiği eğrisinde B noktası VDS değerine pinch-off gerilimi (VP) denir. Herhangi bir JFET için, VP sabit bir değerdir. Görüldüğü gibi, pinch-off geriliminin üzerinde VDS’nin sürekli artışı hemen hemen sabit bir drain akımı sağlar. Drain akımının bu değerine (gate kısa devre iken drain ucundan source ucuna olan akım) IDSS denir ve bütün JFET’ler için ayrıca belirtilir.

IDSS, JFET’in ilave bir devre olmaksızın üretebildiği maksimum drain akımıdır ve bu değer her zaman VGS = 0 V için belirtilir. (b) deki grafiğe bakılırsa, VDS deki artışla beraber ID akımının çok hızlı artmaya başladığı C noktasında bir kırılma oluşur. Bu kırılma, telafisi mümkün olmayan zararlara sebep olur. Bundan dolayı JFET’ler her zaman kırılma geriliminin altında ve sabit akım bölgesinde (grafikteki B ve C noktaları arasında) çalıştırılır.

ID AKIMININ KONTROLÜ

Aşağıdaki şekilde (a) da gösterildiği gibi gate ile source arasına VGG kutuplama kaynağını bağlayalım. VGS gerilimi, VGG kaynağının ayarlanmasıyla daha negatif değerlere çekilirken, drain karakteristikleri de (b) de olduğu gibi elde edilir. Dikkat edilirse, VGS gerilimi daha negatif değerlere arttırılırken ID akımı azalır. Ayrıca, VGS deki her artış için JFET, VP değerinden daha küçük VDS gerilimlerinde pinch-off noktasına (sabit akımın başladığı bölge) ulaşır. Böylece drain akımının miktarı VGS tarafından kontrol edilmiş olur.

KESİM VOLTAJI

ID akımını yaklaşık sıfır yapan VGS gerilimine kesim (cutoff) voltajı, VGS(off) denir. JFET, VGS=0 ve VGS(off) değerleri arasında çalıştırılmalıdır. Bu aralıktaki gate-source gerilimleri için, ID akımı, maksimum değer olan IDSS’den minimum değer olan sıfır arasında değişecektir.

N-kanal JFET için, daha negatif VGS gerilimi, sabit akım bölgesinde daha küçük ID akımı oluşturacaktır. Eğer VGS yeteri kadar büyük bir negatif değer ise, ID akımı sıfıra düşecektir. Bu kesim etkisi, aşağıdaki şekilde gösterildiği gibi, fakirleşmiş bölgenin, kanalın tamamen kapandığı noktaya kadar genişlemesiyle oluşur.

P-kanal JFET’in çalışması da aynen n-kanal JFET’te olduğu gibidir, farklı olarak sadece negatif bir VDD ve pozitif bir VGS gerilimine ihtiyaç duyar.

JFET GİRİŞ DRENCİ ve KAPASİTESİ

JFET, gate-source ekleminin ters kutuplanmasıyla çalışır. Bundan dolayı, gate ucundaki giriş direnci oldukça yüksektir. Bu yüksek giriş direnci, JFET’in bipolar transistörlere karşı bir avantajıdır (bipolar transistörler doğru yönde kutuplanmış beyz-emiter eklemine sahiptir).

Giriş direncini hesaplamak için genellikle kataloglarda verilen belirli bir gate-source voltajındaki ters akım değeri, IGSS, kullanılır ve aşağıdaki formülle hesaplanır.

JFET’in giriş kapasitesi, Ciss, bipolar transistörden daha büyüktür çünkü ters kutuplanmış pn eklemiyle çalışmaktadır.

(Sakarya Üniversitesi)

İlk Yorumu Siz Yapın